Write Invalidate

Ensure that a processor has exclusive access to a data item before it writes that item. Invalidates other copies on a write. It is by far the most common protocol. Exclusive access ensures that no other readable or writable copies of an item exist when the write occurs: All other cached copies of the item are invalidated.

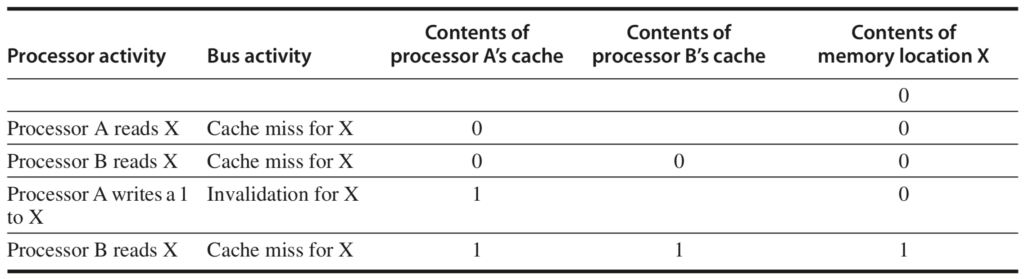

An example of an invalidation protocol working on a snooping bus for a single cache block (X) with write-back cache.

The processor and memory contents show the value after the processor and bus activity have both completed. A blank indicates no activity or no copy cached. When the second miss by B occurs, processor A responds with the value canceling the response from memory. In addition, both the contents of B’s cache and the memory contents of X are updated.

Since the write requires exclusive access, any copy held by the reading processor must be invalidated (hence, the protocol name). Thus, when the read occurs, it misses in the cache and is forced to fetch a new copy of the data. For a write, we require that the writing processor have exclusive access, preventing any other processor from being able to write simultaneously. If two processors do attempt to write the same data simultaneously, one of them wins the race, causing the other processor’s copy to be invalidated. For the other processor to complete its write, it must obtain a new copy of the data, which must now contain the updated value. Therefore, this protocol enforces write serialization.

Write Broadcast

Update all the cached copies of a data item when that item is written. Because a write update protocol must broadcast all writes to shared cache lines, it consumes considerably more bandwidth. For this reason, recent multiprocessors have opted to implement a write invalidate protocol.

Comparision

| Scenario/Metric | Write Invalidate | Write Brodcast |

|---|---|---|

| Multiple writes to same word | 1 invalidation | Multiple write broadcast |

| Writes to different words in same cache block | 1 invalidation | Multiple write broadcast |

| Delay between writing in one core and reading in another | Longer | Shorter |

What if the fourth processor activity is “Processor B updates X”, what will happen?

It will be similar to how Processor A writes X

– Processor B writes a 2 to X

– Invalidation for X

– A’s cache blank

– B’s cache 2

– Memory location still 1

On the next read by A, A’s cache and memory location gets updated to 2