A Write Buffer acts as an intermediary between the Cache and the Main Memory. If the Write Buffer has an empty slot, the data and the address is written to this slot. From the processor’s viewpoint, the write is complete. These slots are called Buffer Entries.

Subsequent reads can be served by the Write Buffer. If the buffer is full and there is no address match, the cache (and processor) must wait until the buffer has an empty entry. The Write Buffer writes back its data onto the Main Memory. This frees up a Buffer Entry.

Buffer Entry

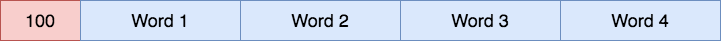

A Buffer Entry has two components – the address and the data. In the following figure one Buffer Entry can hold upto ![]() blue words. This Buffer Entry references the address

blue words. This Buffer Entry references the address ![]() in red.

in red.

Populating the Buffer Entry

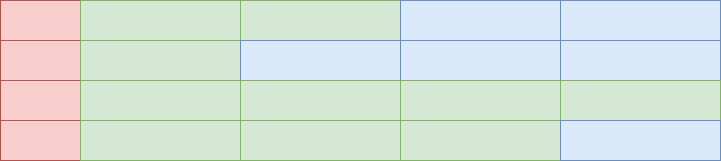

Each Buffer Entry is populated based on the data to be written. It is quite possible that not all the slots in a Buffer Entry are occupied. A slot is occupied only when data needs to be written. In the following figure, only ![]() green words of data needs to be written at the red address. The rest

green words of data needs to be written at the red address. The rest ![]() blue slots are unoccupied.

blue slots are unoccupied.

Write Buffer

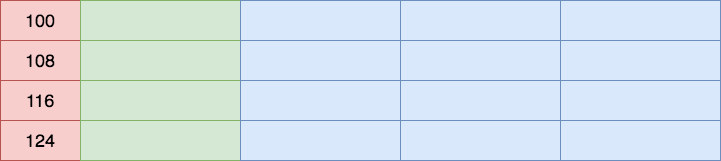

A Write Buffer is made up of many such Buffer Entries. Here is a simple Write Buffer with ![]() Buffer Entries. Different Buffer Entries are at different fractions of occupancy.

Buffer Entries. Different Buffer Entries are at different fractions of occupancy.

Sequential Addresses

Consider the case when the Buffer Entries reference sequential memory addresses. One possible configuration of the Write Buffer is shown below.

The free slots in the first Buffer Entry are not being utilized efficiently. All the Buffer Entries are occupied. The processor now has to stall until these entries are written back to main memory.

Write Merging

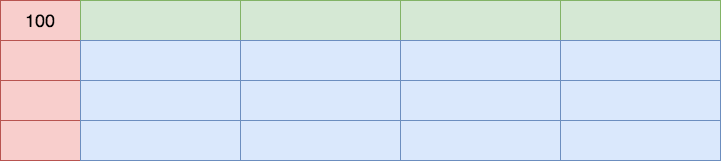

If the buffer already contains other modified blocks, the address of the new data can be compared with existing Buffer Entries. In case of a match, the new data is combined with that entry. This is called Write Merging.

The same data now occupies just a single Buffer Entry. All the other Buffer Entries are free. Thus, this optimization reduces stalls due to the Write Buffer being full. This in turn reduces Miss Penalty.

Pingback: Cache Optimizations that reduce Miss Penalty - TheBeardSage