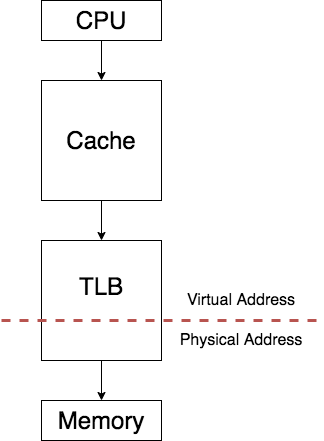

The Cache and the TLB serve as an intermediary between the CPU and memory. Based on the organization, the CPU can access the data in several different ways.

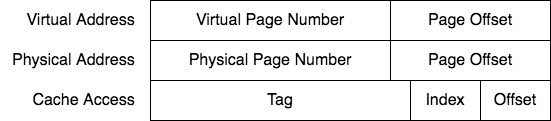

Recall that a TLB converts a Virtual Address to a Physical Address. Cache can be accessed by either Virtual or Physical Address

Physically Indexed Physically Tagged

All memory addresses are translated to physical addresses before the cache is accessed. In this organization, the cache is physically indexed and physically tagged (both the cache index and tag are physical, rather than virtual, addresses).

These are simple to implement but slow. The amount of time to access memory, assuming a cache hit, must accommodate both a TLB access and a cache access.

Virtually Indexed Virtually Tagged

A cache that is accessed with a virtual address rather than a physical address. In such caches, the TLB is unused during the normal cache access, since the cache is accessed with a virtual address that has not been translated to a physical address.

This organization takes the TLB out of the critical path, reducing cache latency. When a cache miss occurs, however, the processor needs to translate the address to a physical address so that it can fetch the cache block from main memory.

Issues with Virtually Addresed Caches

- Context Switch Every time a process is switched, the virtual addresses refer to different physical addresses, requiring the cache to be flushed.

- Aliasing Operating systems and user programs may use two different virtual addresses for the same physical address. These duplicate addresses, called synonyms or aliases, could result in two copies of the same data in a virtual cache. This ambiguity would allow one program to write the data without the other program being aware that the data had changed.

Virtually Indexed Physically Tagged

In this configuration the cache uses the virtual address for the index and the physical address for the tag comprision.

Recall that the page offset portion of the address remains unchanged while converting a Virtual Address to a Physical Address. These bits can be used to index into the cache.

At the same time as the cache is being read using that index, the virtual part of the address is translated to a physical address. The tag comparision uses this physical addresses.

To pull it off, there must be careful coordination between the minimum page size, the cache size, and associativity. The bits used to index the Cache must entirely come from the Page Offset.

If ![]() , the cache index bits come only from page offset (same in Virtual Address and Physical Address). Here the Cache indexing operation and the TLB translation can proceed in parallel.

, the cache index bits come only from page offset (same in Virtual Address and Physical Address). Here the Cache indexing operation and the TLB translation can proceed in parallel.

If ![]() , some of the cache index bits come from the Virtual Page Number. The indexing operation has to wait until these bits are translated to their Physical Page Number counterparts.

, some of the cache index bits come from the Virtual Page Number. The indexing operation has to wait until these bits are translated to their Physical Page Number counterparts.